Genel Sorular

- Yaptığınız projelerden bahsedin

Dijital Tasarım

- Metastability nedir?

- İki farklı clock domain’i var. Bunlar arasında veri transferi nasıl yaparsın?

- Asenkron FIFO?

- Setup-Hold?

- Clock, jitter?

- Elinde 100 MHz Clock var. Öyle bir ihtiyaç var ki 50MHz lik clock üretilmeli, nasıl yapılır? 75 MHz’de nasıl yapabiliriz?

- 10 tane 32 bitlik sayı paralel olarak modüle geliyor. En hızlı toplayıcı devresini çiziniz? İstediğin kadar toplayıcı kullanılabilir.

- Vivado ortamında bir tasarımın 120 MHz’e sentezlenmesi isteniyor. Bu gereksinim için nasıl yapılmaktadır? (Constraint file XDC)

- Sadece MUX kullanarak bir AND kapısı tasarlayınız.

- SERDES yapısı nedir?

- Transceiver yapısı nedir?

- DDR nedir?

- Fixed point ve floating point sayı farkı?

- MRCC vs SRCC (Clock Capable)

Doğrulama

- Doğrulama konusundaki çalışmalar?

- SystemVerilog

- UVM

IP Tabanlı Tasarımlar

- PLL nedir?

- AXI arayüzü hakkında bilgi?

- AXI arayüzlerinde master ve slave kavramlarını açıkla

- VDMA?

- Microblaze

- AXI Interconnect

- UART, SPI, I2C, Ethernet, PCIe, HDMI, VGA, Display Port arayüzleri ile çalışma

Çizim

- Clock /2 divider devresini çizip, RTL’ini yazınız

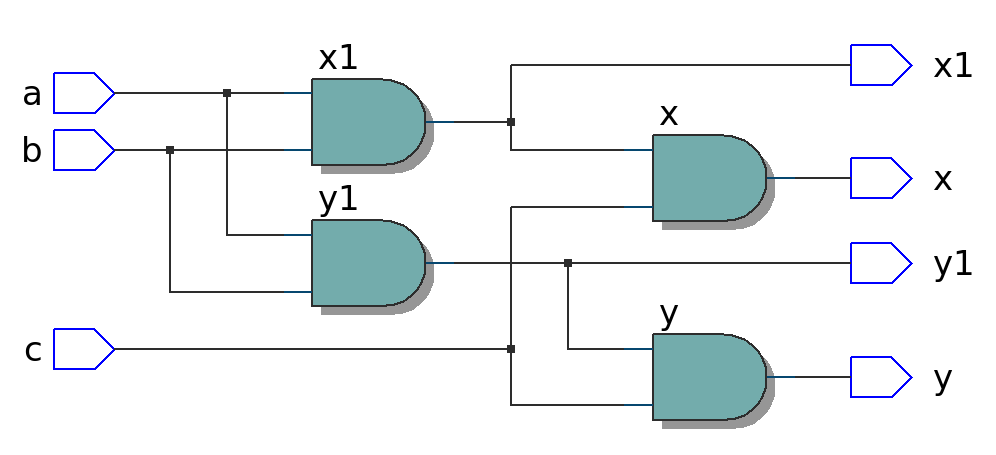

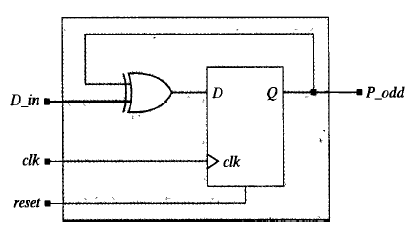

- Aşağıda verilen kombinasyonel devrenin Verilog dilindeki gösterimini yazınız.

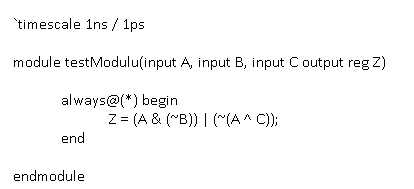

- Aşağıda verilen Verilog RTL kodunun karşılığı olan donanım’ın şematik çizimini yapınız.

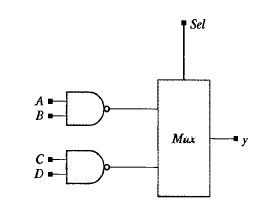

- Aşağıda verilen devrenin Verilog gösterimindeki karşılığını yazınız. A, B, C, D ve Sel sinyalleri giriş, y sinyali ise çıkıştır

- D tipi tutucu (latch) ve D tipi saklayıcı (Register) nedir? Arasındaki farklar nedir?

- Saat kristali nedir?

- Clock sinyali nedir? Ne için kullanılır?

- Periyodu 100 ns olan bir clock’un frekansı nedir?

- Ardışık devreler neden kullanılır? Neden kombinasyonel devreler ile bazı işlemler gerçekleştirilemiyor?

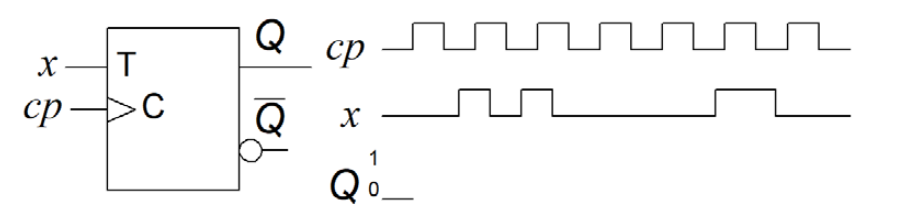

- Aşağıda verilen D tipi yükselen kenar tetiklenen saklayıcıya gelen cp (clock) ve x sinyaline göre Q çıkışından çıkması gereken sinyali çiziniz.

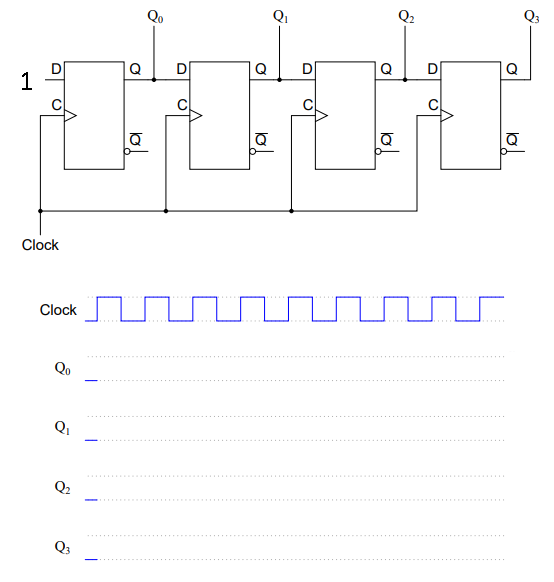

- Aşağıdaki devrede 4 adet d tipi saklayıcı kullanılmıştır. Devre uzun bir süre d girişinden 0 verilerek çalıştırılmış ve başlangıçta q0, q1, q2 ve q3 0 olarak çıktı vermektedir. Devrenin girişi 1’e dönüştürüldüğü andan itibaren, aşağıdaki dalga formunu doldurunuz.

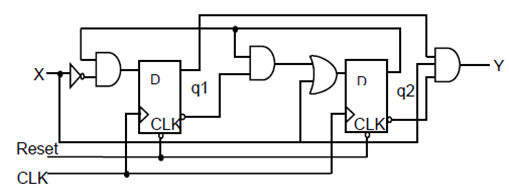

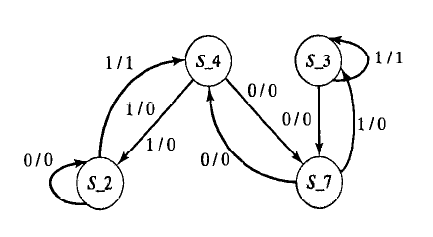

- Aşağıda verilen ardışık devreye belirli bir giriş dizisi verildiğinde 1 değerini üretmektedir (Pattern Checker). Verilmiş olan 4 pattern’den hangisinin 1 değerini ürettirebileceğini tespit ediniz. Başlangıçta saklayıcıların değerlerini 0 olarak alınız.

A -) 0110

B -) 1001

C -) 0100

D -) 1101

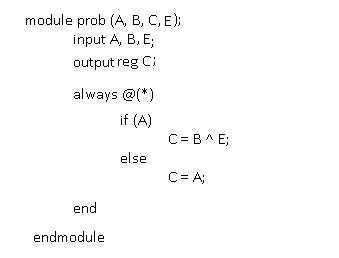

- Aşağıda verilen Verilog RTL kodunu sentezlendiği zaman ortaya çıkacak devreyi çiziniz.

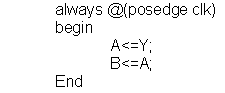

- Aşağıda verilen verilog kod parçacığı sentezlenince oluşacak donanım şematiğini çiziniz.

- Aşağıda verilen devrenin Verilog gösterimini yazınız.

Sonlu Durum Makinaları

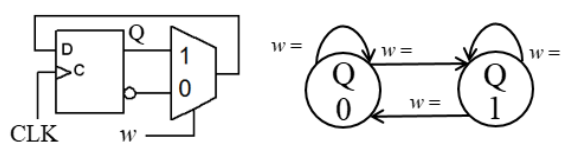

- Aşağıda D tipi saklayıcı ve MUX barındıran bir devre bulunmaktadır.

Yanında ise bu devrenin durum makinaları ile ifade edilmiş hali bulunmaktadır. Q0 durumu Q çıkışının 0 verdiği, Q1 durumu ise Q çıkışının 1 verdiği durumu temsil etmektedir. Q çıkışı 0 verir iken, w girişi ne gelmelidir ki Q yine 0 çıkmaya devam etsin? Bu durumu Q0’ın kendi üstüne ok ile döndüğü yerdeki w = yerine yazmalısınız. Bu mantık ile w= olan yerleri tamamlayınız. - Aşağıda verilen Mealy durum makinasının Verilog dilinde gerçekleyiniz.

Tasarım Sorusu

- Reverse Polish Notation

http://www.levent.tc/files/mulakat/reversePolishNotation.rar

Xilinx Based

- HLS

- Vitis

- Vitis Vision Library

- Vitis AI Library

- Vitis BLAS, Fintech, and OpenCV

- Modelcomposer (Matlab Based)

- Xilinx Runtime Library (XRT)

- RFSOC

- MPSOC (VCU)

- Versal ACAP

Software Mülakat Soruları

- Pointer

- Public, Private, Protected

- Struct, Class, Kalıtım, polymorphism

- Görüntü işleme ?

Kütüphaneler, OpenCV - GPU programming, CUDA, OpenCL

- C++ STL Kütüphane, Vector, Queue

- Exception handling

- Yapay zeka

- Petalinux, Embedded

- FFmpeg, Gstreamer

- Problem, sniper detection:

http://www.levent.tc/files/mulakat/demo.mp4 - ASCPE http://www.levent.tc/files/courses/tools/sinavsistemi/