Course Description: Bu ders kapsamında gömülü sistemlerde kullanılan bir Linux dağıtımı olan Petalinux ile çalışılacaktır. Ders’te Xilinx’in PYNQ Z2 geliştirme kartlar kullanılacaktır. Dönem projesi olarak CORDIC (COordinate Rotation DIgital Computer) IP’si kullanıldığı ve işlemcinin hesap yükünü donanım hızlandırıcıya aktardığı bir proje yapılacaktır. Petalinux Ortamından Uart arayüzü üzerinden yakalanan veriler CORDIC IP’sile iletilip, sonuçları Uart üzerinden PC’e iletilecektir.

Category: Courses

Microcontrollers

Course Description: Bu ders kapsamında mikrokontrolör mimarisi kullanılarak robot kontrol algoritmaları geliştirilecektir. Ders kapsamında bir sumo robot kiti üzerinde deneyler gerçekleştirilecektir. Dönem projesi olarak sumo robot gerçeklenip, verilecek 5 adet hedefin 60 saniye içerisinde platformdan atabilecek bir sumo robot algoritması geliştirilecektir.

Interfaces II

- lwIP kütüphanesi ile UDP haberleşme örneği aşağıdaki linkte verilmektedir.

https://github.com/Xilinx/embeddedsw/blob/master/lib/sw_apps/lwip_udp_perf_server/src/udp_perf_server.c

bu kod parçacığında 162-260. satırlar arasında UDP paketi yakalandığında çağrılan callback fonksiyonu bulunmaktadır. Fonksiyonu modifiye ederek, Ethernetten içerisinde ‘S,’E’,’L’,’A’,’M’ byte’ı barıdıran bir paket geldiğinde, geriye ‘M,’E’,’R,’H,’A,’B’,’A’ byte’larını gönderen bir uygulama geliştiriniz. - MAC adresi nedir?

- TCP ve UDP arasındaki farklar nedir?

Microblaze

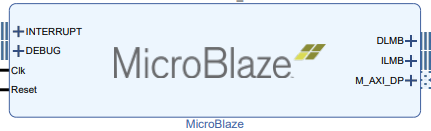

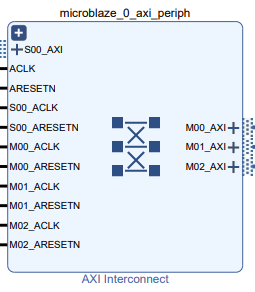

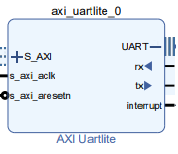

- Aşağıda Microblaze, uartlite ve AXI Interconnect IP’lerinin giriş ve çıkış arayüzleri verilmiştir.

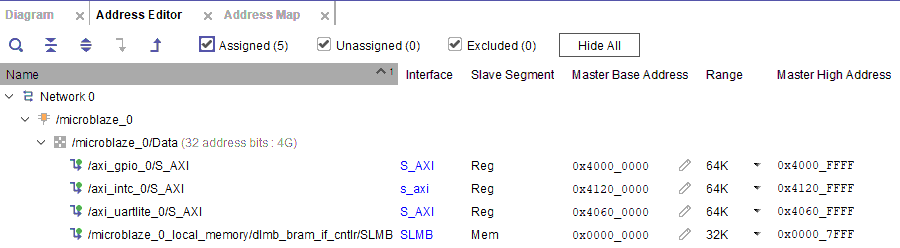

Bu üç IP’i birbirlerine bağlayarak microblaze’in UART paketleri gönderebileceği sistemi oluşturunuz. Diğer (Örn, DLMB, ILMB) bağlantıların çizilmesine gerek yoktur. - Aşağıda blok diyagramda tasarlanmış olan bir microblaze tabanlı sistemin Adress Editor pencere görüntüsü bulunmaktadır.

Microblaze’e bağlı olan GPIO IP’sinin giriş bölümüne 8 bitlik bir switch bağlanmış, çıkış bölümüne ise LED’ler bağlanmıştır. AXI GPIO’nun saklayıcı listesi aşağıda verilmektedir.

Bu sistem için, CPU üzerinde switch’lerden alınan değerin bir fazlasını LED’lerde gösterecek bir kod parçacığı geliştiriniz. - AXI Interrupt Controller IP’sinin görevi nedir?

- Microblaze gibi softcore bir işlemci hangi durumlarda kullanılması tercih edilebilir? Hardcore bir işlemciye göre avantaj ve dezavantajlarını sıralayınız.

Performance Profiling and Debugging

- Breakpoint nedir? Ne amaçla kullanılır?

- Profiler Tool nedir?

- Bir yazılımda en yavaş çalışan fonksiyonu bulmak için izlenebilecek stratejiler nedir?

QEMU

- QEMU nedir?

- Bir emulatör kullanmanın avantaj ve dezavantajları nedir?

Final Sample Questions

Donanım Doğrulama Metodları (DDM): Sınıflar

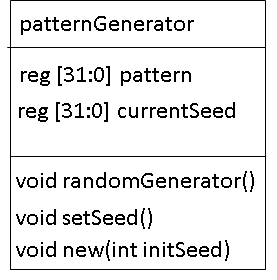

- patternGenerator isminde bir sınıf oluşturunuz. Sınıfın UML Diagramı aşağıda verilmektedir.

Sınıfta 2 adet 32 bitlik pattern ve currentSeed isimli saklayıcı bulunmaktadır. Sınıfın constructor’u int türünde initSeed isminde bir argüman almakta ve aldığı argümanı currentSeed saklayıcısına yazmaktadır. setSeed fonksiyonu currentSeed değerini sabit olarak 32’h1234 değerine atamaktadır. randomGenerator fonksiyonu ise aşağıda verilen operasyonu gerçekleştirmektedir.

void randomGenerator() {

pattern = currentSeed;

pattern = pattern ^ ( pattern << 13);

pattern = pattern ^ ( pattern >> 17);

pattern = pattern ^ ( pattern << 5);

currentSeed = pattern;

}

patternGenerator sınıfından testbench modülünde bir obje türetip, constructor’una 1234 decimal sayısını veriniz. Ardından pattern degiskenini $display ile ekrana gösteriniz. randomGenerator fonksiyonunu çağırıp pattern değişkenini $display ile ekrana gösteriniz.

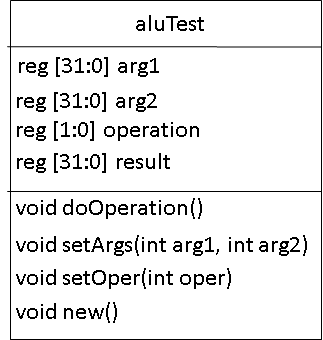

- aluTest isimli bir sınıf geliştiriniz. Bu sınıfın UML diyagramı aşağıda verilmektedir.

Bu sınıf içerisinde arg1, arg2, operation ve result isminde 4 adet saklayıcı barındırmaktadır. arg1, arg2 ve result 32 bitlik, operation ise 2 bitliktir. Sınıftın constructor’u bir argüman almamakta ve constructor çalıştığında sınıfta bulunan tüm değişkenlere sıfır değerini atamaktadır. setOper fonksiyonu bir argüman alıp, aldığı argümanı operation değişkenine atamaktadır. setArgs fonksiyonu iki argüman alıp, aldığı argümanları arg1 ve arg2 değişkenlerine atamaktadır. doOperation fonksiyonu argüman almaktadır. Bu fonksiyon sınıfın içindeki operation saklayıcısının değerine göre aşağıda verilen işlemleri yapmaktadır.

operation == 0 –> result = arg1 + arg2

operation == 1 –> result = arg1 – arg2

operation == 2 –> result = arg1 * arg2

operation == 3 –> result = arg1 & arg2

aluTest sınıfını tasarladıktan sonra, aluTest sınıfını kullanan bir testbench hazırlayınız. Bu testbench ile aluTest sınıfının yapabildiği 4 farklı operasyonu test etmelidir.

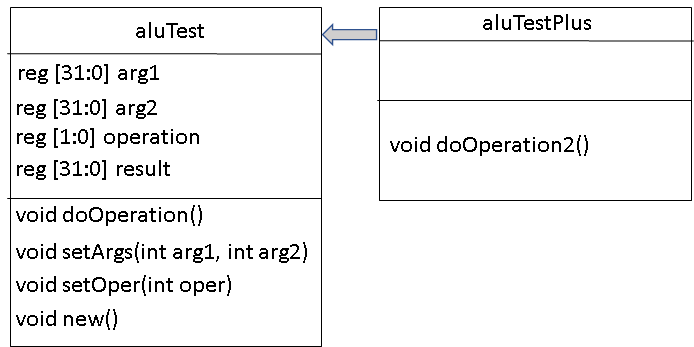

DDM: Kalıtım

- aluTest sınıfından kalıtım yapılarak aluTestPlus isminde bir sınıf oluşturunuz. Bu sınıfın içerisinde ek bir fonksiyon olarak doOperations2 isimli bir fonksiyon bulunmalıdır. Sınıfın UML diyagramı aşağıda verilmekedir.

doOperations2 fonksiyonu operation değişkenine bakarak aşağıda verilen operasyonları yapmaktadır.

operation == 0 –> result = arg1 | arg2

operation == 1 –> result = arg1 ^ arg2

operation == 2 –> result = arg1 + 1

operation == 3 –> result = arg2 + 1

aluTestPlus sınıfını tasarladıktan sonra, aluTestPlus sınıfını kullanan bir testbench hazırlayınız. Bu testbench ile aluTestPlus sınıfının yapabildiği 8 farklı operasyonu test etmelidir.

DDM: Değişken Türleri

- aluTestPlus sınıfından aluTestPlus2 isimli bir sınıf kalıtım yapınız. Bu sınıfın içerisinde void doOperation3(string argIn1, string argIn2, string operationIn) isimli bir fonksiyon bulunmaktadır. Bu fonksiyon aldığı string argIn1 ve argIn2 argümanlarından herhangi biri floating point ise (yani string’in içinde nokta işareti varsa) aşağıda verilen operasyonları yapmaktadır.

operationIn == 0 –> result = argIn1 * argIn1

operationIn == 1 –> result = argIn1+ arg2

operationIn == 2 –> result = argIn1 – 1

operationIn == 3 –> result = arg2 + 1

eğer string argIn1 ve argIn2 argümanları floating point değiller ise (yani string içinde nokta işareti yok ise) aşağıda verilen operasyonları yapmaktadır.

operationIn == 0 –> result = argIn1 – argIn2

operationIn == 1 –> result = argIn1* arg2

operationIn == 2 –> result = argIn1 – 5

operationIn == 3 –> result = arg2 + 5

aluTestPlus2 sınıfını tasarladıktan sonra, aluTestPlus2 sınıfını kullanan bir testbench hazırlayınız. Bu testbench ile aluTestPlus sınıfının yapabildiği 8 farklı operasyonu test etmelidir.

DDM: Arayüzler

- modul1 ve modul2 isminde iki modül tanımlaması yapınız. Bu modüllere ortak olarak giren ve çıkan sinyaller aşağıda verilmektedir.

* clk

* rst

* data[31:0]

* wrEn

verilen 4 sinyali gruplayarak myIntf isimli bir interface tanımlaması yapınız. Bu interface’i her iki modül için kullanınız. Ayrıca modul2 için out isminde bir bitlik çıktı vardır. modul1 her clock cycle data sinyalinin değerini bir arttırarak dışarıya sürmektedir. wrEn sinyalini ise sabit olarak 1 olarak sürmektedir. rst geldiği zaman ise data sinyalini 0’a atamaktadır. Modül 2 wrEn sinyali aktif iken kendine gelen data sinyalinin değeri 100 ise, out çıkışından 1 sinyali çıkartmaktadır. Eğer rst sinyali aktif ise out çıktısı 0 olmalıdır.

Bir testbench ortamı geliştirip modul1 ve modul2’in sahip olduğu myIntf interface’ini birbirine bağlayınız. Clock’u interface’e testbench’ten besleyiniz. - Modport nedir? Ne amaçla kullanılmaktadır?

DDM: Rasgeleleştirme

- rand ve ranc nedir? Aralarındaki fark nedir? Örnek vererek açıklayınız.

- randomUretici isimli bir sınıf tasarlayınız. Bu sınıfta 2 bitlik bir rand türünde rasgele isimli bir saklayıcı tanımlayınız. Bu değişkenin rasgele üretimi esnasında 0 sayısının üretilmemesi için bir constraint tanımı yapınız. randomUretici sınıfından bir obje türetip, initial/begin bloğu içerisinde randomize fonksiyonunu 10 defa döngü ile çağırıp üretilen rasgele değerleri $display ile ekranda gösteriniz.

Midterm Sample Questions

Elektriğe Giriş ve Dirençler

- Pozitif ve negatif polarite nedir?

- İletkenlik, yalıtkanlık ve yarı iletkenlik kavramları nedir?

- Direnç nedir?

- Kapalı ve açık devre kavramları nedir?

- Doğru ve alternatif akım nedir?

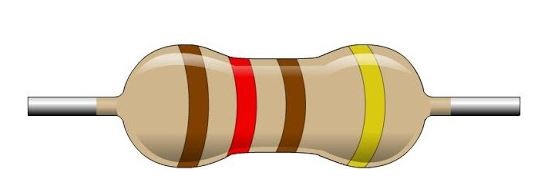

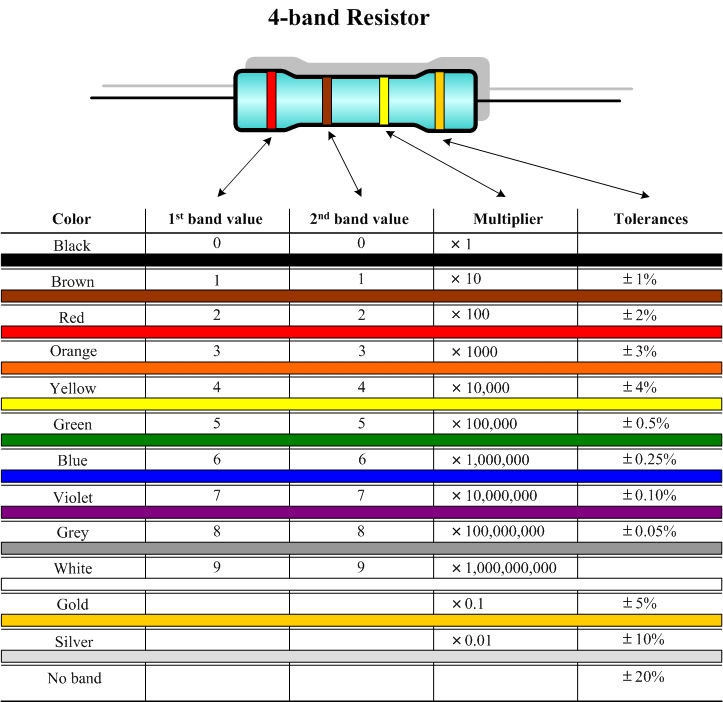

- Aşağıda verilen direnç renk tablosuna göre ve verilmiş direncin renk kodlarından Ohm değerini hesaplayınız.

- Sıfır ohm’luk dirençler neden kullanılmaktadır?

Ohm Yasası

- 1000 Ohm’luk bir direncin üzerinden 0.01 amper akım geçebilmesi için kaç Volt’luk bir gerilim uygulanmalıdır?

- Bir motor 120 Volt altında 2 amperlik bir akım çekmektedir. Bu motorun direnci nedir?

- Bir klima 220 V altında 20 amper akım çekmete ise, bu klimanın tükettiği güç’ü hesaplayınız.

- Bir elektrik süpürgesi 220V altında 15 amper akım çekmektedir. Elektrik kullanılan bölgede kilowatt saat fiyatı 2 TL ise, bu süpürge 2 saat çalıştırıldığında elektrik faturasına kaç TL eklenecektir?

Seri Devreler

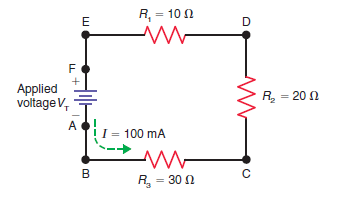

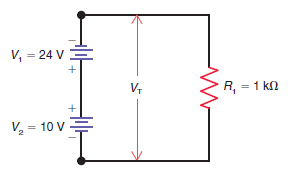

- Aşağıda verilen devredeki direnç ve devrede dönen akım’a göre gerilim kaynağının gerilim değerini hesaplayınız.

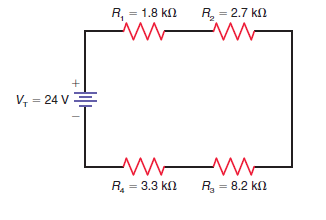

- Verilen devrenin üzerinden geçen akımı hesaplayınız.

- Verilen devredeki gerilim kaynağının gerilim değerini hesaplayınız.

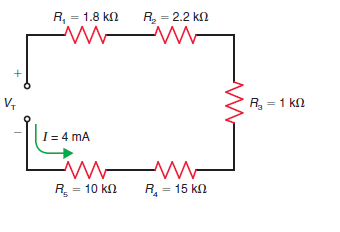

- Verilen devredeki geçen akımı hesaplayınız.

Paralel Devreler

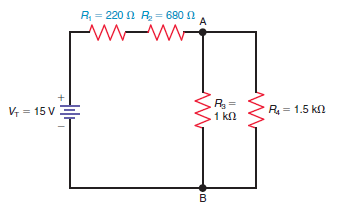

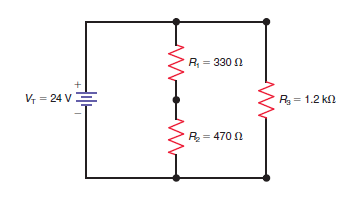

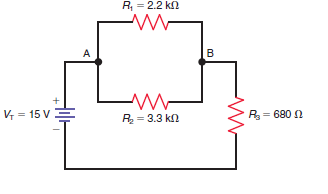

- Aşağıda verilen devrenin üzerinden geçen toplam akımı ve R3, R4 dirençleri üzerinden geçen akımları hesaplayınız.

- Aşağıda verilen devredeki R1 ve R2 dirençleri üzerine düşen gerilimleri ve R3 direnci üzerinden geçen akımı hesaplayınız.

- Aşağıda verilen devrede R1 ve R2 dirençleri üzerinden geçen akımı ve R3 direnci üzerine düşen gerilimi hesaplayınız.

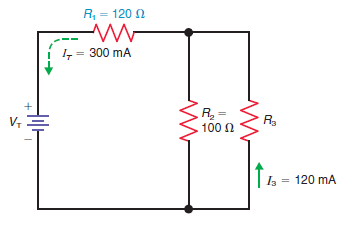

- Devrede verilen akım değerlerine göre gerilim kaynağının gerilim değerini ve R3 direncinin Ohm değerini hesaplayınız.

RTL Design

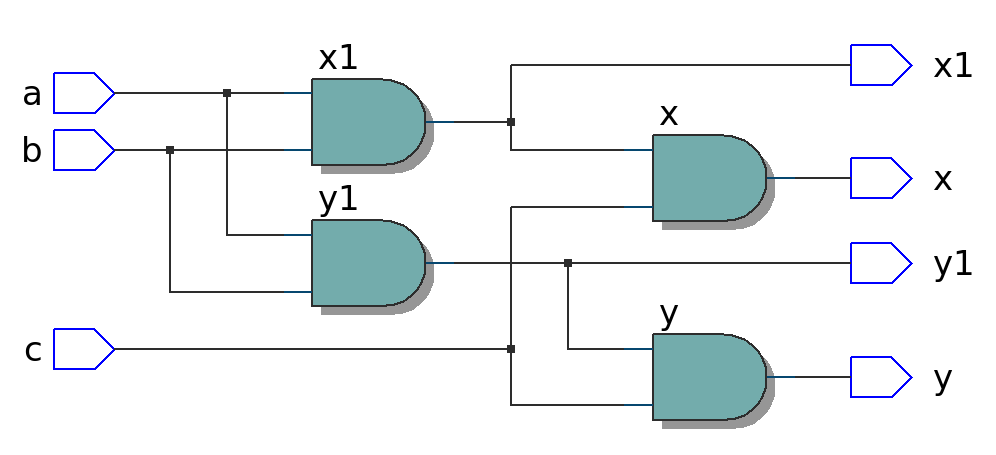

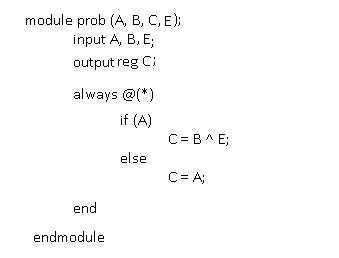

- Aşağıda verilen kombinasyonel devrenin Verilog dilindeki gösterimini yazınız.

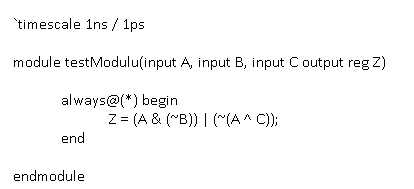

- Aşağıda verilen Verilog RTL kodunun karşılığı olan donanım’ın şematik çizimini yapınız.

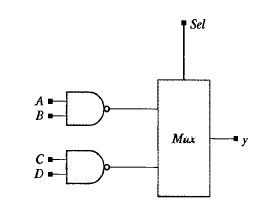

- Aşağıda verilen devrenin Verilog gösterimindeki karşılığını yazınız. A, B, C, D ve Sel sinyalleri giriş, y sinyali ise çıkıştır

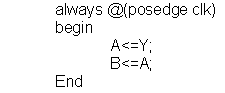

- Aşağıda verilen Verilog RTL kodunu sentezlendiği zaman ortaya çıkacak devreyi çiziniz.

- Aşağıda verilen verilog kod parçacığı sentezlenince oluşacak donanım şematiğini çiziniz.

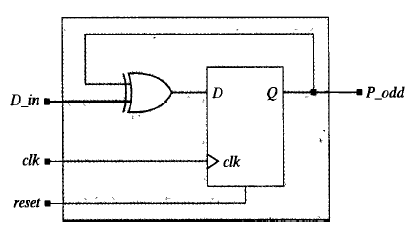

- Aşağıda verilen devrenin Verilog gösterimini yazınız.

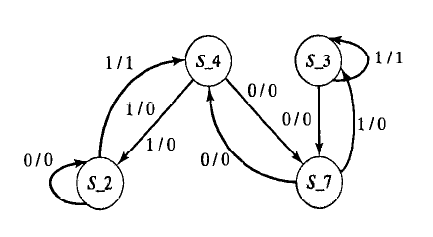

- Aşağıda verilen Mealy durum makinasının Verilog dilinde gerçekleyiniz.

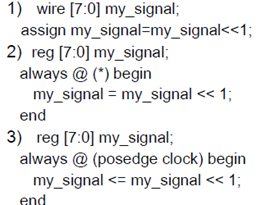

- Aşağıda verilen 3 Verilog kod parçacığı farklı shifter tasarımlarıdır. Hangi tasarımın kombinasyonel hangisinin ardışık devreler ile gerçeklendiğini ifade edip, devrelerini çiziniz. Not: Tasarımda normalde kullanmayı tercih etmediğimiz, kombinasyonel döngü olabilir. Kaydırma devresini kutu olarak çizebilirsiniz.

- 4 farklı operasyon yapabilen iki 4’er bitlik sayı girişi alan bir ALU tasarlanacaktır. Operasyonlar; toplama, cıkartma, çarpma ve 0 üretmektir (Operasyon kodu 3 olduğunda sonuç 0 olacaktır). Operasyon kodu girişi bulunmakta ve 2 bitliktir. ALU tasarımını verilog dilinde yapınız

ZYNQ Mimarisi

- PS ve PL kavramları nedir?

- Microblaze nedir? PS’den farkı nedir?

- APU nedir? APU’da bulunan I-Cache, D-Cache ve L2 Cache’in görevlerini açıklayınız?

- MIO nedir? Ne amaçla kullanılır?

- EMIO nedir? Ne amaçla kullanılır?

- ZYNQ mimarisinde bulunan GP, HP ve ACP portları nedir? Aralarındaki fark nedir?

- Cache Coherence nedir? Bu ihtiyaç için ZYNQ mimarisindeki çözüm nedir? Olası sorunu bir örnek ile açıklayıp, çözümü anlatınız.

- ZYNQ mimarisindeki NEON Engine nedir?

Veriyolları

- AXI arayüzü nedir? Kim tarafından geliştirilmiştir?

- AXI gibi bir arayüzü modüller arasında iletişim için kullanmanın avantajı nedir?

- Xilinx ortamında kullanılan AXI türlerini açıklayınız.

- AXI Lite ve AXI MM arayüzleri arasındaki farkı açıklayınız.

- Master ve Slave kavramlarını açıklayınız?

- AXI Lite ve AXI MM veriyolu üzerinde bulunan 5 kanalın isimleri ve görevleri nelerdir?

- AXI arayüzlerindeki ready sinyali ne işe yaramaktadır?

- AXI arayüzlerindeki valid sinyali ne işe yaramaktadır?

Interfaces

- UART arayüzü nasıl çalışmaktadır?

- SPI arayüzü nasıl çalışmaktadır?

- I2C arayüzü nasıl çalışmaktadır?

- Aşağıda verilen Xilinx Github Reposunda bulunan UART loopback örneğinde, UART portundan 32 byte’lık veri transfer edilip, geriye alınıp aynı sonucun gelip gelmediği kontrol edilmektedir.

https://github.com/Xilinx/embeddedsw/blob/master/XilinxProcessorIPLib/drivers/uartps/examples/xuartps_polled_example.c

Bu örneğin dışarıdan gelecek 100 UART paketini toplayıp, sonucunu geriye UART hattından döndürecek şekilde değiştiriniz.

LMS and Piazza

Öğrencilerin soru sorup yanıt alabileceği bir soru cevap sistemi sunulmaktadır. Ders duyuruları, öğrenci soruları ve cevapları için bir platformdur. Aşağıdan erişebilirsiniz.

https://piazza.com/class/kre5vtyygs7is

Blackboard (Learning Management System), bazı ödevlerin teslimi için LMS sistemi üzerinden olması istenecektir.

https://blackboard.fbu.edu.tr/

Labs

Uzaktan LAB bağlantısı: fpga.levent.tc

Project

CORDIC Tabanlı HW/SW CoDesign: Donanım hızlandırıcı olarak Xilinx’in CORDIC (COordinate Rotation DIgital Computer) IP’si kullanıldığı ve işlemcinin hesap yükünü donanım hızlandırıcıya aktardığı bir proje yapılacaktır

Proje detayları için tıklayınız.