Donanım Doğrulama Metodları (DDM): Sınıflar

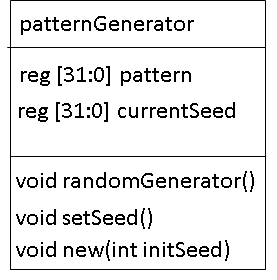

- patternGenerator isminde bir sınıf oluşturunuz. Sınıfın UML Diagramı aşağıda verilmektedir.

Sınıfta 2 adet 32 bitlik pattern ve currentSeed isimli saklayıcı bulunmaktadır. Sınıfın constructor’u int türünde initSeed isminde bir argüman almakta ve aldığı argümanı currentSeed saklayıcısına yazmaktadır. setSeed fonksiyonu currentSeed değerini sabit olarak 32’h1234 değerine atamaktadır. randomGenerator fonksiyonu ise aşağıda verilen operasyonu gerçekleştirmektedir.

void randomGenerator() {

pattern = currentSeed;

pattern = pattern ^ ( pattern << 13);

pattern = pattern ^ ( pattern >> 17);

pattern = pattern ^ ( pattern << 5);

currentSeed = pattern;

}

patternGenerator sınıfından testbench modülünde bir obje türetip, constructor’una 1234 decimal sayısını veriniz. Ardından pattern degiskenini $display ile ekrana gösteriniz. randomGenerator fonksiyonunu çağırıp pattern değişkenini $display ile ekrana gösteriniz.

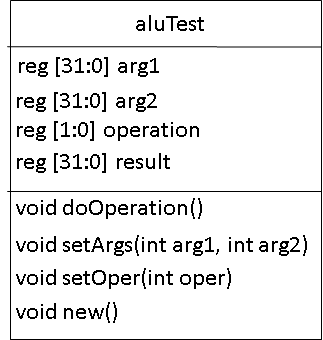

- aluTest isimli bir sınıf geliştiriniz. Bu sınıfın UML diyagramı aşağıda verilmektedir.

Bu sınıf içerisinde arg1, arg2, operation ve result isminde 4 adet saklayıcı barındırmaktadır. arg1, arg2 ve result 32 bitlik, operation ise 2 bitliktir. Sınıftın constructor’u bir argüman almamakta ve constructor çalıştığında sınıfta bulunan tüm değişkenlere sıfır değerini atamaktadır. setOper fonksiyonu bir argüman alıp, aldığı argümanı operation değişkenine atamaktadır. setArgs fonksiyonu iki argüman alıp, aldığı argümanları arg1 ve arg2 değişkenlerine atamaktadır. doOperation fonksiyonu argüman almaktadır. Bu fonksiyon sınıfın içindeki operation saklayıcısının değerine göre aşağıda verilen işlemleri yapmaktadır.

operation == 0 –> result = arg1 + arg2

operation == 1 –> result = arg1 – arg2

operation == 2 –> result = arg1 * arg2

operation == 3 –> result = arg1 & arg2

aluTest sınıfını tasarladıktan sonra, aluTest sınıfını kullanan bir testbench hazırlayınız. Bu testbench ile aluTest sınıfının yapabildiği 4 farklı operasyonu test etmelidir.

DDM: Kalıtım

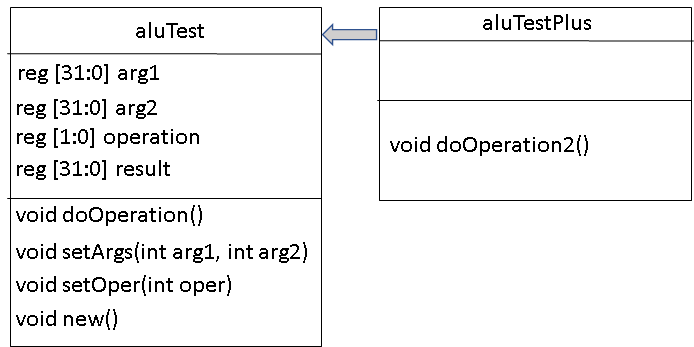

- aluTest sınıfından kalıtım yapılarak aluTestPlus isminde bir sınıf oluşturunuz. Bu sınıfın içerisinde ek bir fonksiyon olarak doOperations2 isimli bir fonksiyon bulunmalıdır. Sınıfın UML diyagramı aşağıda verilmekedir.

doOperations2 fonksiyonu operation değişkenine bakarak aşağıda verilen operasyonları yapmaktadır.

operation == 0 –> result = arg1 | arg2

operation == 1 –> result = arg1 ^ arg2

operation == 2 –> result = arg1 + 1

operation == 3 –> result = arg2 + 1

aluTestPlus sınıfını tasarladıktan sonra, aluTestPlus sınıfını kullanan bir testbench hazırlayınız. Bu testbench ile aluTestPlus sınıfının yapabildiği 8 farklı operasyonu test etmelidir.

DDM: Değişken Türleri

- aluTestPlus sınıfından aluTestPlus2 isimli bir sınıf kalıtım yapınız. Bu sınıfın içerisinde void doOperation3(string argIn1, string argIn2, string operationIn) isimli bir fonksiyon bulunmaktadır. Bu fonksiyon aldığı string argIn1 ve argIn2 argümanlarından herhangi biri floating point ise (yani string’in içinde nokta işareti varsa) aşağıda verilen operasyonları yapmaktadır.

operationIn == 0 –> result = argIn1 * argIn1

operationIn == 1 –> result = argIn1+ arg2

operationIn == 2 –> result = argIn1 – 1

operationIn == 3 –> result = arg2 + 1

eğer string argIn1 ve argIn2 argümanları floating point değiller ise (yani string içinde nokta işareti yok ise) aşağıda verilen operasyonları yapmaktadır.

operationIn == 0 –> result = argIn1 – argIn2

operationIn == 1 –> result = argIn1* arg2

operationIn == 2 –> result = argIn1 – 5

operationIn == 3 –> result = arg2 + 5

aluTestPlus2 sınıfını tasarladıktan sonra, aluTestPlus2 sınıfını kullanan bir testbench hazırlayınız. Bu testbench ile aluTestPlus sınıfının yapabildiği 8 farklı operasyonu test etmelidir.

DDM: Arayüzler

- modul1 ve modul2 isminde iki modül tanımlaması yapınız. Bu modüllere ortak olarak giren ve çıkan sinyaller aşağıda verilmektedir.

* clk

* rst

* data[31:0]

* wrEn

verilen 4 sinyali gruplayarak myIntf isimli bir interface tanımlaması yapınız. Bu interface’i her iki modül için kullanınız. Ayrıca modul2 için out isminde bir bitlik çıktı vardır. modul1 her clock cycle data sinyalinin değerini bir arttırarak dışarıya sürmektedir. wrEn sinyalini ise sabit olarak 1 olarak sürmektedir. rst geldiği zaman ise data sinyalini 0’a atamaktadır. Modül 2 wrEn sinyali aktif iken kendine gelen data sinyalinin değeri 100 ise, out çıkışından 1 sinyali çıkartmaktadır. Eğer rst sinyali aktif ise out çıktısı 0 olmalıdır.

Bir testbench ortamı geliştirip modul1 ve modul2’in sahip olduğu myIntf interface’ini birbirine bağlayınız. Clock’u interface’e testbench’ten besleyiniz. - Modport nedir? Ne amaçla kullanılmaktadır?

DDM: Rasgeleleştirme

- rand ve ranc nedir? Aralarındaki fark nedir? Örnek vererek açıklayınız.

- randomUretici isimli bir sınıf tasarlayınız. Bu sınıfta 2 bitlik bir rand türünde rasgele isimli bir saklayıcı tanımlayınız. Bu değişkenin rasgele üretimi esnasında 0 sayısının üretilmemesi için bir constraint tanımı yapınız. randomUretici sınıfından bir obje türetip, initial/begin bloğu içerisinde randomize fonksiyonunu 10 defa döngü ile çağırıp üretilen rasgele değerleri $display ile ekranda gösteriniz.